I hold a MSc in Electrical Engineering from the State University of Campinas (UNICAMP) and a BSc in Electrical Engineering from the Federal University of Rio Grande do Norte (UFRN). I specialise mostly in digital image processing and machine learning, with a focus on tasks like super-resolution and restoration. My other interests include image/video compression, hardware design, embedded systems, etc...

AVIF vs JPEG XL - A comparison between state of the art image formats on anime-style art

Super Resolution Part I - An introduction to ML image upscaling

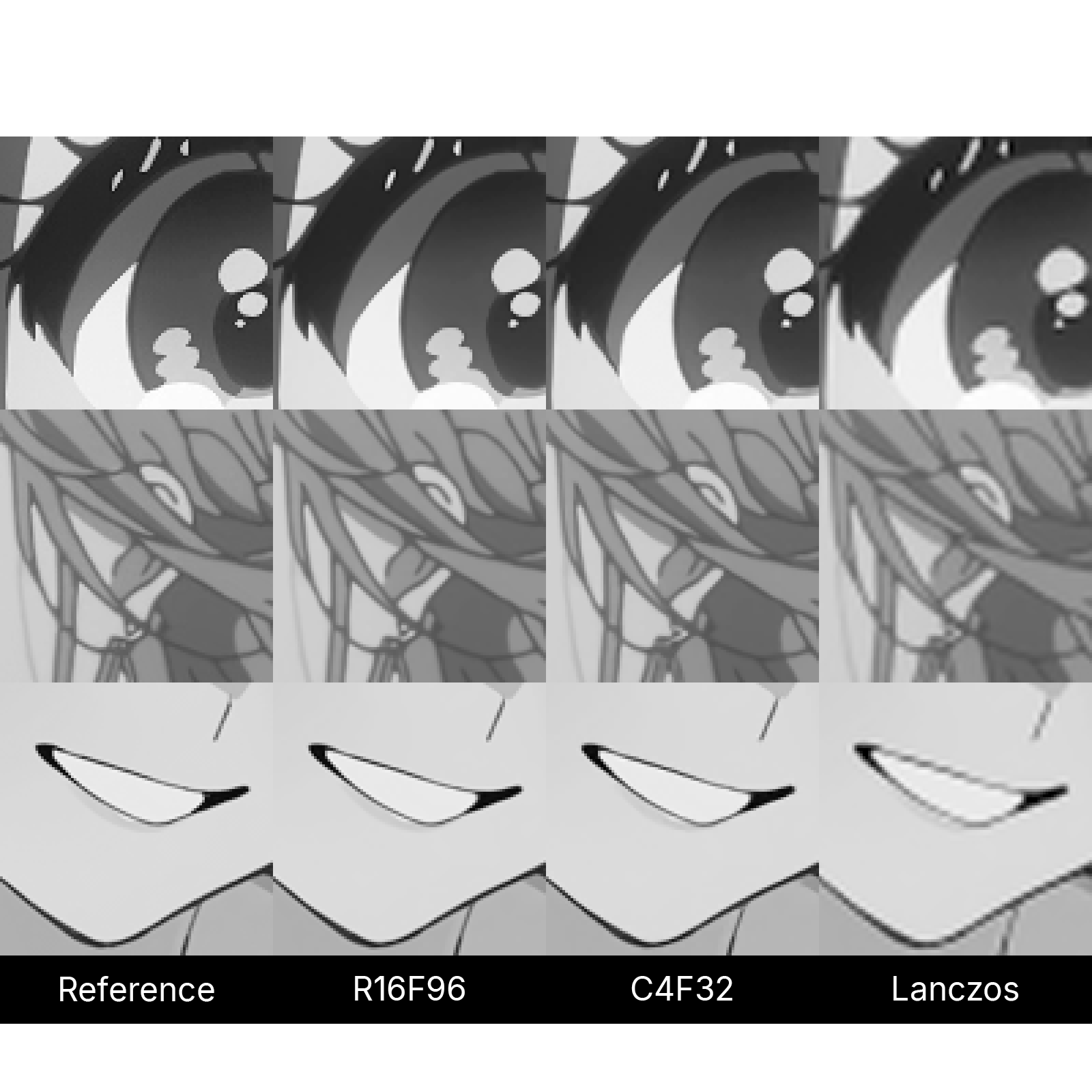

mpv Resampling - A sequel in the making

ImageMagick Resampling - When doing it with mpv isn't enough...

Gamma Correction - Why you should care

Building a RISC-V CPU Core - An introduction to Computer Architecture and Digital Design

Interning at the Brazilian National Institute for Space Research

Assigned to work alongside Wind River on their distributed edge cloud infrastructure.

Assigned to work alongside Motorola on ISP pipelines, imaging algorithms and auto-focus for camera systems in Android devices.

Assigned primarily at developing and maintaining the testbench of a SBCDA (Brazilian Environmental Data Collection System) Cubesat compatible payload, including a hardware in the loop test-routine

and the required code to emulate an on-board-computer utilising an x86 Workstation running Matlab as a master, an Arduino Due as an I²C bridge and a Rohde&Schwarz SMBV100A Vector Signal Generator.

Secondary tasks varied from firmware development to brainstorming possible engineering solutions or improvements to the Environmental Data Collector as a whole,

which included changes to the dedicated decoding hardware in the Microsemi Smartfusion 2 FPGA, or to the communication protocols handled by the ARM Cortex-M3 based microcontroller subsystem running FreeRTOS.

My work is about accelerating Convolutional Neural Networks for real-time super-resolution on integrated GPUs.

My grad level classes included internet of things, digital signal processing and machine learning.

Developed Maestro, a 5-stage pipeline in-order RV32I RISC-V core written entirely in VHDL for academic purposes. Intel Quartus Prime and ModelSim were utilised for synthesis and verification, and a Cyclone V FPGA was used for testing purposes. The core is part of my bachelor’s degree and can be found at https://riscv.org/risc-v-cores.

Undergrad classes included digital and analogue electronics, power systems, control systems, communication systems, embedded systems and artificial intelligence.

Convolutional Neural Networks for super-resolution and restoration of anime-style art. Available as GLSL shaders and in the ONNX format.

View Project

CfL is a GLSL shader that implements chroma upscaling based on the closed least squares solution for linear regression, inspired by the adoption of the same technique in modern video codecs.

View ProjectPixel Clipper is a GLSL shader for anti-ringing. It limits pixel magnitude after resampling to avoid overshooting and haloing.

View Project

Maestro is a 5 stage pipeline implementation of the RV32I ISA strongly inspired by David Patterson's and John Hennessy's Computer Organization and Design RISC-V Edition.

The project is entirely academic, it's written in VHDL in a beginner-friendly way so computer architecture students can also learn about hardware design.